As some of you know, I am dealing with a health condition that requires brain surgery, scheduled for the next three months. This period of waiting and preparation has been an emotional journey, full of reflections and moments of introspection.

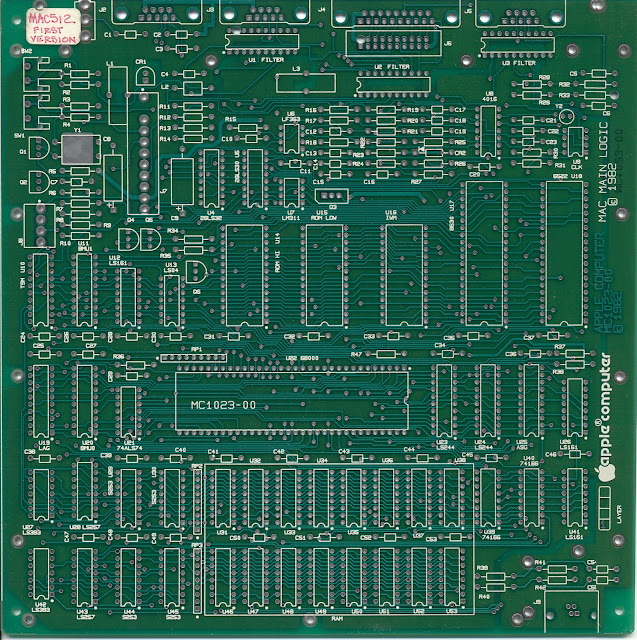

During these months, I have experienced a range of emotions: from tiredness to sadness, from doubts to hope. These feelings have affected not only my daily life, but also my ability to focus on the Macintosh 128k replica project and keep this blog updated.

In this period of preparation for the surgery, I am learning to balance my commitment to the project with the need to take care of my health. This led me to reflect on the importance of accepting and sharing my vulnerability, not only as an act of personal courage, but also as a way to connect with others who may find themselves in similar situations.

However, I will continue to share updates when possible, because this project and this blog are important parts of my journey.

Thank you for your understanding, patience and continued support. I hope to soon share positive news and new progress on our journey together in the world of technology and innovation.